### **Description**

The KLR9193 Series are highly precise,low noise,positive voltage LDO regulators manufactured using CMOS processes. The KLR9193 performance is optimized for battery-powered systems to deliver ultra low noise and low quiescent current. Regulator ground current increases only slightly in dropout, further prolonging the battery life. The KLR9193 Series also works with low-ESR ceramic capacitors, reducing the amount of board space necessary for power applications, critical in handheld wireless devices. The KLR9193 Series consumes less than 1µA in shutdown mode and has fast turn-on time less than 50µs.

The other features include ultra low dropout voltage, high output accuracy, current limiting protection, and high ripple rejection ratio.

#### **Features**

- Ultra Low Noise for RF Application

- ◆ Ultra Fast Response in Line/Load Transient

- Low Power Consumption:70uA(Typ.)

- ◆ PSRR=70dB@1KHz

- Maximum Output Current: 300mA

- ◆ Low Dropout : 130mV @ 100mA at V<sub>OUT</sub>=3.3V

- ◆ Operating Voltage Ranges : 2V to 6.5V

- Over Temperature Protection

- Current Limiting Protection

- Thermal Shutdown Protection

## **Applications**

- ◆ Battery-Powered Equipment

- ◆ CDMA/GSM Cellular Handsets

- Portable Information Appliances

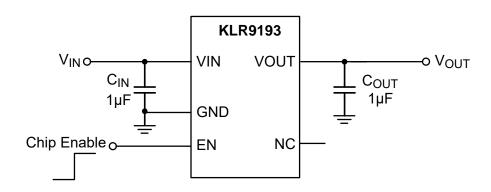

## **Typical Application Circuit**

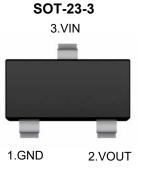

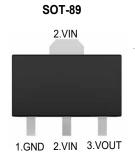

## **Functional Pin Description**

| Pin Name | Pin Function                                                    |

|----------|-----------------------------------------------------------------|

| EN       | Chip Enable (Active High). Note that this pin is high impedance |

| NC       | NO Connected                                                    |

| GND      | Ground.                                                         |

| VOUT     | Output Voltage.                                                 |

| VIN      | Power Input Voltage.                                            |

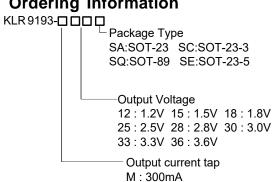

### Marking Code:

9193

XX: Output Voltage

12:1.2V 15:1.5V 18:1.8V 25:2.5V 28:2.8V 30:3.0V

33:3.3V 36:3.6V

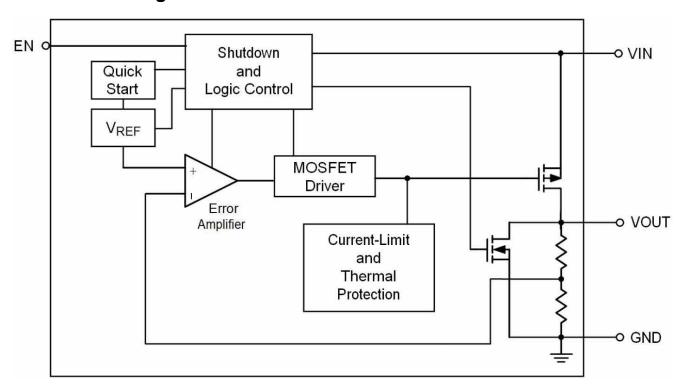

# **Function Block Diagram**

## Absolute Maximum Ratings Note1

Ratings at 25°C ambient temperature unless otherwise specified.

| Parameter                               | Value               | Unit     |      |

|-----------------------------------------|---------------------|----------|------|

| Input Valtage                           | V <sub>IN</sub>     | -0.3~7   | V    |

| Input Voltage                           | V <sub>ON/OFF</sub> | -0.3~0.3 | V    |

| Output Voltage                          | Output Voltage      |          | V    |

|                                         | SOT-23              | 300      | mW   |

|                                         | SOT-23-3            | 250      | mW   |

| Power Dissipation                       | SOT-23-5            | 250      | mW   |

|                                         | SOT-89              | 400      | mW   |

|                                         | SOT-23              | 330      | °C/W |

|                                         | SOT-23-3            | 400      | °C/W |

| Thermal Resistance, Junction-to-Ambient | SOT-23-5            | 400      | °C/W |

|                                         | SOT-89              | 250      | °C/W |

| Operating Ambient Temperature           |                     | -40~85   | ℃    |

| Maximum Junction Temperature            |                     | 260      | °C   |

| Storage temperature range               |                     | -40~125  | °C   |

| ESD(HBM) Note2                          |                     | 4        | KV   |

| ESD(CDM) Note2                          |                     | 400      | V    |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **2.** ESD testing is performed according to the respective JESD22 JEDEC standard. The human body model is a 100pF capacitor discharged through a  $1.5K\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

| Parameter                               | Value   | Unit |

|-----------------------------------------|---------|------|

| Supply Voltage                          | 2~6.5   | V    |

| Operating Junction Temperature Range,Tj | -40~125 | °C   |

| Operating Free Air Temperature Range,TA | -40~85  | °C   |

### **Electrical Characteristics**

(V<sub>IN</sub>=V<sub>OUT</sub>+1, V<sub>OUT</sub> = 3.3V, C<sub>IN</sub>=C<sub>OUT</sub>=1 $\mu$ F, T<sub>A</sub>=25°C , unless otherwise noted.)

| Pa                                        | rameter         | Symbol             | Conditions                                                             | MIN. | TYP. | MAX. | Unit              |

|-------------------------------------------|-----------------|--------------------|------------------------------------------------------------------------|------|------|------|-------------------|

| Input Voltage                             |                 | V <sub>IN</sub>    |                                                                        | -0.3 |      | 6.5  | V                 |

| Output Vo                                 | oltage Accuracy | $\Delta V_{OUT}$   | I <sub>OUT</sub> =40mA                                                 | -2   |      | +2   | %                 |

| Quiescent Current                         |                 | ΙQ                 | $V_{IN}>V_{OUT}$ , $EN=V_{IN}$ $I_{OUT}=0$ mA                          |      | 70   |      | μA                |

| D                                         |                 | V <sub>DROP</sub>  | I <sub>OUT</sub> =100mA                                                |      | 130  |      | mV                |

| <b>Бторс</b>                              | Dropout Voltage |                    | I <sub>OUT</sub> =200mA                                                |      | 250  |      |                   |

| Line Regulation                           |                 | $\Delta V_{LINE}$  | V <sub>IN</sub> =V <sub>OUT</sub> +1V to 7V<br>I <sub>OUT</sub> =40mA  |      | 0.05 |      | %/V               |

| Load Regulation                           |                 | $\Delta V_{LOAD}$  | 1mA <i<sub>OUT&lt;100mA</i<sub>                                        |      | 50   |      | mV                |

| Output Voltage<br>Temperature Coefficient |                 | TC <sub>VOUT</sub> | I <sub>OUT</sub> =10mA                                                 |      | 100  |      | ppm/°C            |

| Short circuit/start carrying current      |                 | I <sub>SHORT</sub> | RL=1Ω                                                                  |      | 50   |      | mA                |

| EN Leakage Current                        |                 | I <sub>EN</sub>    |                                                                        |      | 1    |      | μA                |

| Cui                                       | Current Limit   |                    | V <sub>IN</sub> =V <sub>OUT</sub> +1                                   |      | 450  |      | mA                |

| EN                                        | Logic Low       | V <sub>IL</sub>    | V <sub>IN</sub> =3V to 5.5V,<br>Shutdown                               |      |      | 0.4  | V                 |

| Input<br>Threshold                        | Logic High      | V <sub>IH</sub>    | V <sub>IN</sub> =3V to 5.5V,<br>Start up                               | 1.2  |      |      | V                 |

| Output Noise<br>Voltage                   |                 | e <sub>NO</sub>    | 300Hz to 50KHz,<br>I <sub>OUT</sub> =40mA                              |      | 50   |      | μV <sub>RMS</sub> |

| Power Supply Rejection Rate               |                 | PSRR               | V <sub>IN</sub> =V <sub>OUT</sub> +1<br>I <sub>OUT</sub> =40mA, f=1KHz |      | 70   |      | dB                |

### **Applications Information**

### **Input Capacitor**

A 1µF ceramic capacitor is recommended to connect between VIN and GND pins to decouple input power supply glitch and noise. The amount of the capacitance may be increased without limit. This input capacitor must be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both VIN and GND.

#### **Output Capacitor**

An output capacitor is required for the stability of the LDO. The recommended minimum output capacitance is  $1\mu F$ , ceramic capacitor is recommended, and temperature characteristics are X7R or X5R. Higher capacitance values help to improve load/line transient response. The output capacitance may be increased to keep low undershoot/overshoot. Place output capacitor as close as possible to VOUT and GND pins.

#### **Enable Function**

The KLR9193 Series has an EN pin to turn on or turn off the regulator, When the EN pin is in logic high, the regulator will be turned on. The shutdown current is almost 0µA typical. The EN pin may be directly tied to VIN to keep the part on. The Enable input is CMOS logic and cannot be left floating.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$PD(MAX) = (TJ(MAX) - TA) / R\theta JA$$

Where TJ(MAX) is the maximum operation junction temperature 125°C, TA is the ambient temperature and the R $\theta$ JA is the junction to ambient thermal resistance.

The power dissipation definition in device is:

$$PD = (VIN - VOUT) \times IOUT + VIN \times IQ$$

## **Layout Consideration**

By placing input and output capacitors on the same side of the PCB as the LDO, and placing them as close as is practical to the package can achieve the best performance. The ground connections for input and output capacitors must be back to the KLR9193 Series ground pin using as wide and as short of a copper trace as is practical. Connections using long trace lengths, narrow trace widths, and connections through via must be avoided. These add parasitic inductances and resistance that results in worse performance especially during transient conditions.

# Package Outline

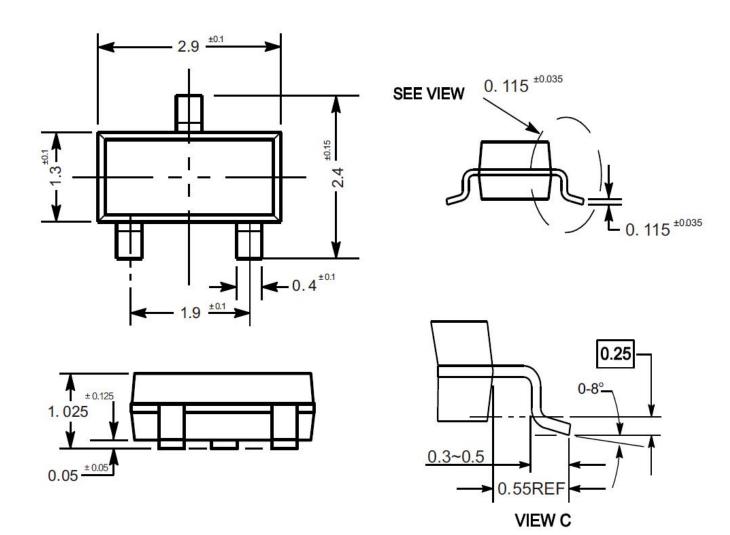

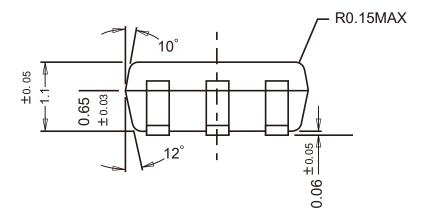

SOT-23

Dimensions in mm

| Device         | Package | Shipping                      |

|----------------|---------|-------------------------------|

| KLR9193 Series | SOT-23  | 3,000/ Tape & Reel (7 inches) |

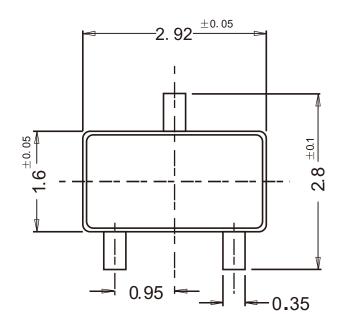

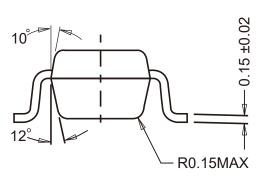

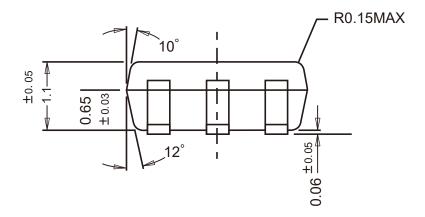

## **Package Outline**

SOT-23-3

Dimensions in mm

## **Ordering Information**

| Device         | Package  | Shipping                      |

|----------------|----------|-------------------------------|

| KLR9193 Series | SOT-23-3 | 3,000/ Tape & Reel (7 inches) |

9

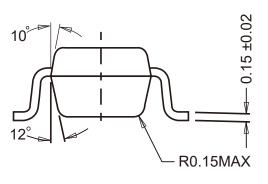

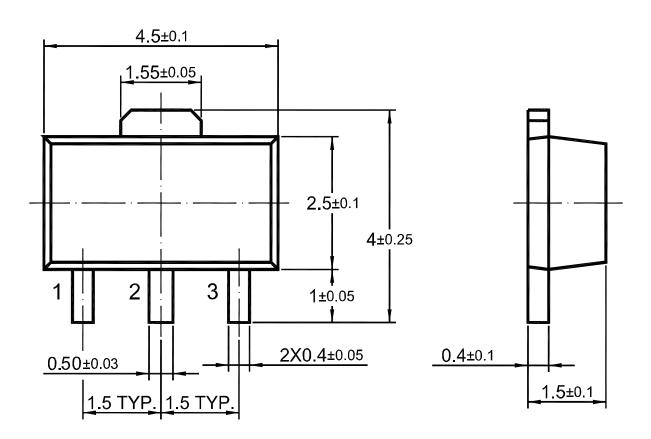

# Package Outline

SOT-89

Dimensions in mm

| Device         | Package | Shipping                  |

|----------------|---------|---------------------------|

| KLR9193 Series | SOT-89  | 1,000PCS/Reel&Tape(7inch) |

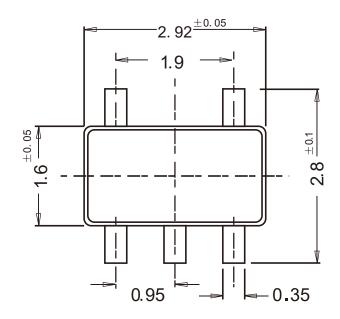

## Package Outline

SOT-23-5

Dimensions in mm

| Device         | Package  | Shipping                      |

|----------------|----------|-------------------------------|

| KLR9193 Series | SOT-23-5 | 3,000/ Tape & Reel (7 inches) |